Computer System= Hardware+ Software

Hardware:-Physical Components (We can touch and seen).

Software:-Logical Components (We can seen and do work something according to object/goal).

**Computer Organization:-**

#### What Is Computer:-

Making for Calculations as well as measurement

Based on Arithmetical and Logical.

Arithmetic/Numeric Operation (+, -, \*, /, ^, % (modulo operator/Remainder Operator)).

Logical Operation (True, False, Yes, No).

**General Definition 1:-**

It (Computer) can perform only those operations or calculations (Arithmetical and Logical), Measurement and controlling functions, which can be expressed there, result in terms of numerical or logical.

#### Program:-

The basic function/task/work of computer is the execution of program.

It is sequence of <u>instructions</u>, which operate on computer <u>data</u> to perform certain well-defined task or achieve a goal.

**Data:-** It is facts and figure that is represented in the form of 0 and 1. It is known as <u>Bits</u>(Binary Digits).

### **Modern Definition 2:-**

It is an automatic electronic apparatus/Machine making for controlling operations and performing arithmetical and logical operations and can also perform measurement. Which can be expressed there result in terms of numerical or logical.

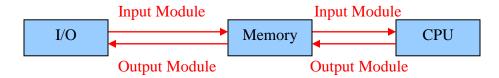

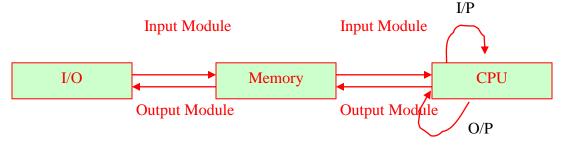

#### **Structure of Computer**

Structure of computer was given by Von Neumann. He was a British mathematician

**Input Gives**→ **instructions & data after Ouput**→**Produce Result (Numerical or Logical)**

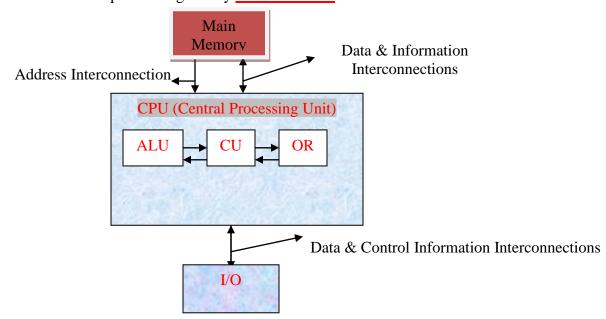

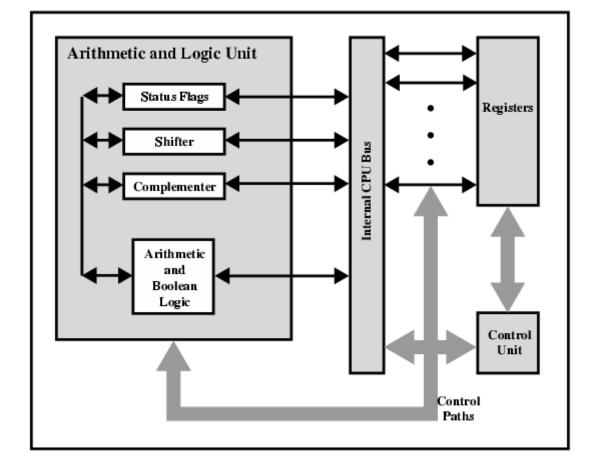

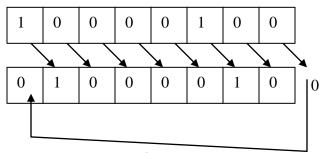

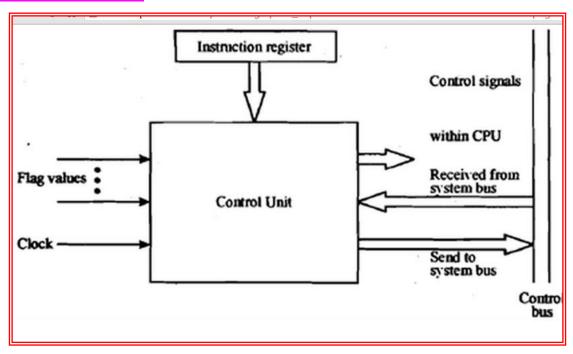

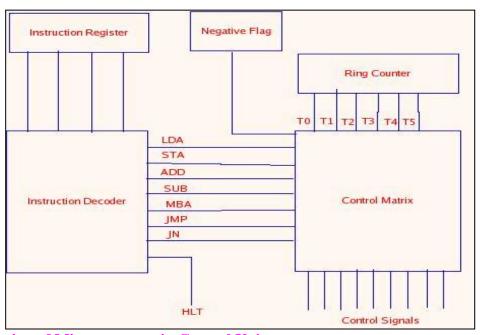

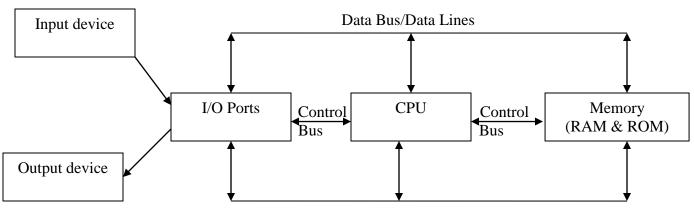

## **CPU:-**It is the **brain** of computer which consist of following three components ❖ ALU:- By This unit it can perform all types of arithmetical and logical operations ❖ CU:- It is used for controlling operations inside CPU. It accept signal from out side & produce their corresponding signal. It is the heart of computer. It is a special type of temporary storage area where actual processing is to be performed by CPU. **❖** OR:-The size of register determines processing speed of CPU. Processing speed measured in MIPS. (Million Instruction Per Seconds) as well as hertz unit. ALU :-Arithmetic & Logic unit. CU :-Control Unit. OR :-Operational Register. Main Memory:-It is needed in a computer to store instructions and the data at the time of program execution. Computer data represented in the form of 0 and 1.It is known as bits (Binary digits). 0 Off/false/No. On/true/Yes. 1 8 bits=One Byte. One Byte=One Character. Example:-ICSM=4 Bytes=32 4\*8=Bits. 1 Kilo Byte (KB) =1024 Bytes=2<sup>10</sup> Bytes. 1 Mega Byte (MB) =1024 \*1024Bytes=2<sup>20</sup> Bytes. 1 Giga Byte (GB) =1024\*1024\*1024 Bytes=2<sup>30</sup> Bytes. 1 Tera Byte (TB) =1024\*1024\*1024 \*1024 Bytes=2<sup>40</sup> Bytes. 1 Peta Byte (PB) =1024\*1024\*1024 \*1024\* 1024Bytes=2<sup>50</sup> Bytes. 1 Exabyte (EB) = $2^{60}$ Bytes. 1 Zettabyte (ZB) = $2^{70}$ Bytes. 1 Yottabyte (YB) = $2^{80}$ Bytes.

Notes:-Bits was invented by Lady ada. She had written first program of computer.

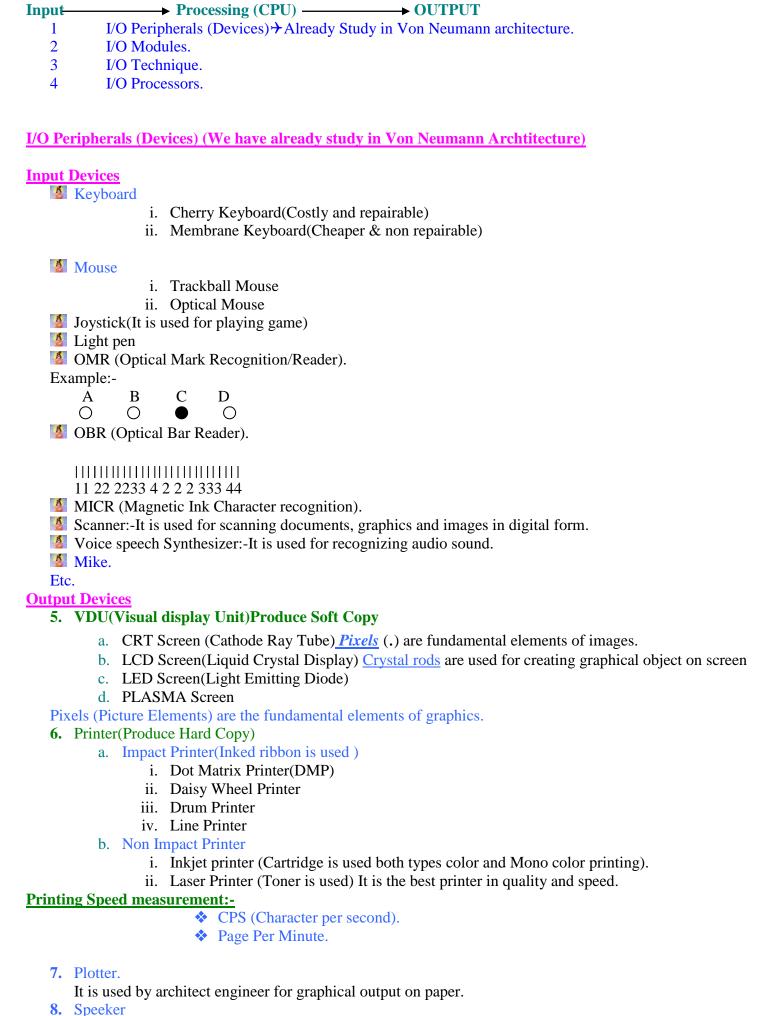

#### I/O Devices: (Input/Output Devices)

## **Input Devices**(Instructions and Data)

Keyboard

- i. Cherry Keyboard (Costly and repairable).

- ii. Membranes Keyboard (Cheaper & non repairable).

- Mouse

- i. Trackball Mouse.

- ii. Optical Mouse.(Better Quality).

- Joystick. (It is used for playing game).

- Light pen.(It is used for drawing on screen directly).

- Mark Recognition/Reader).

Example:-

Marks on papers. Optical Bar Reader). It is used for identification of items. It interprets pencil marks on papers.

- MICR (Magnetic Ink Character recognition/Reader). → It is used in banking industry.

- Scanner:-It is used for scanning documents, graphics and images in digital form.

- Voice Speech Synthesizer:-It is used for recognizing audio sound/voice.(Used in cockpit of airlines).

- Mike.

Etc.

#### **Output Devices:-**

- 1. VDU(Visual Display Unit)Produce Soft Copy/Electronic mode copy

- a. CRT Screen (Cathode Ray Tube) Pixels (.) are fundamental elements of images.

- b. LCD Screen (Liquid Crystal Display) <u>Crystal rods</u> are used for creating graphical object on screen.

- c. LED Screen (Light Emitting Diode).

- d. PLASMA Screen.

- 2. Printer(Produce Hard Copy).

- a. Impact Printer (Inked ribbon is used).

- i. Dot Matrix Printer (DMP). (It prints only mono /single color).

- ii. Daisy Wheel Printer.

- iii. Drum Printer.

- iv. Line Printer.

- b. Non Impact Printer(Used chemical for printing).

- i. Inkjet printer (Cartridge is used). It print both types color and Mono color).

- ii. Laser Printer (Toner is used)It is the best printer in quality and speed.

#### **Printing Speed measurement:-**

- **CPS** (Character per Second).

- ❖ PPM (Page per Minute).

- **3.** Plotter.

It is used by architect engineer for graphical output on paper/Flex.

**4.** Speeker(It produces Sound).

Etc.

#### **Both Input/Output devices:-**

MODEM (Modulator & Demodulator).

It is used for internet connection.

Analog Signal ← → Digital Signal.

Analog Signal (Sine wave)

010 10

Digital Signal (Bit Trains).

- \* Touch Screen.

- Communication Port.

#### **Characteristics of Computer:-**

- Speed.

- \* Accuracy.

- Memory.

- High Remembering power.

- Deligency.

- ❖ No Intelligency.

- **\*** Emotionless.

- Feeling less.

- Versatility.

#### **Types of Computer:-**

- ❖ Analog Computer (Consist of Analog Signal).

- ❖ Digital Computer (Consist of Digital Signal).

❖ Hybrid Computer (Consist of both types of signal).

#### **Analog Computer:-**

Such types of computers are used for measuring temperature, pressure, speed etc.

#### Example:-

Thermometer: It is used for measuring temperature.

Speedometer :- It is used for measuring speed.

Barometer :- It is used for measuring pressure of air.

### <u>Digital Computer</u>→ <u>Classification Of computer</u>:-

- Micro Computer.

- Mini Computer.

- Mainframe Computer.

- Super Computer.

## **Micro Computer:-**

It is small computer, which is used for personal work.

#### **Example:-**

- PC (Personal Computer)/Desktop PC.

- **A** Laptop.

- **\*** Tablet.

- **A** Palmtop.

Etc.

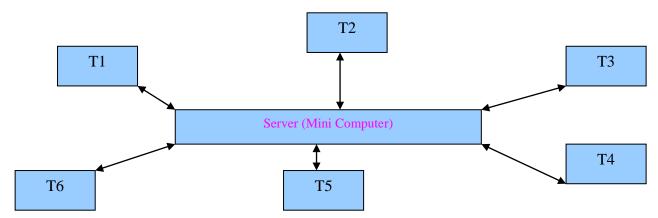

#### Mini Computer:-

It is larger than microcomputer which is used for small networking purpose. It may support 30 to 50 Terminals simultaneously. Example:-PDP-8,Wi-Fi(Wire -Fidelity), Small networking system in bank.

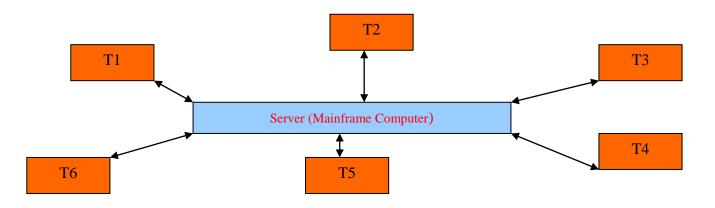

#### **Mainframe Computer:-**

It is also used for networking purpose. It is suited for big organization.

It may support above 500 terminals simultaneously.

#### Example:-

MEDHA. DEC.

SPERRY etc.

#### **Installation Arrangements:-**

- ✓ Arrangements of Power.

- ✓ Arrangement of Special room and environment.

- ✓ Cost of Mainframes exists between 40000\$ to 1 Million dollar.

- ✓ Arrangement of LAN for making large network.

- ✓ Arrangement of computer professionals for working on terminal.

#### **Super Computer:-**

It is the fastest computing device, which is used for solving complex problems. There are many CPU are used in Super Computer.

#### Example:-

PARAM PADMA.

CORAY.

INDIGINIOUS, Hitachi, EKKA.

Etc.

## **Application of Super Computer:**

- ❖ Airlines Controlling.

- **\*** Weather forecasting.

- ❖ Shuttle space controlling. (Atalantice, Colambia).

- Medical Science.

- ❖ Satellite controlling.

Etc

#### **Hybrid Computer:-**

It is made by taking the best features of the analog computer and digital computer. It is used in Hospital, Nuclear controlling system, Hydrogenic System.

#### **Number System (Computer Data Representation Technique):-**

✓ Binary Number System

• 0 and 1 Base /Radix=2.

✓ Octal Number System

• Numbers 0, 1,2,3,4,5,6,7 Base/Radix=8.

✓ <u>Decimal Number System</u>

• Numbers 0,1,2,3,4,5,6,7,8,9 Base/Radix=10.

- **✓** Hexadecimal Number System

- Numbers 0,1,2,3,4,5,6,7,8,9,10,11,12,13,14,15 Base/Radix=16/H.

- 10=A,11=B,12=C,13=D,14=E,15=F

## **Conversion:**

#### **Decimal To Binary Numbers System**

- ✓ Division Method

- ✓ Tabular Method

- ... 2048 1024 512 256 128 64 32 16 8 4 2 1

```

Division Method:-

Example (123)_{10} = (?)_2

Remainder

2

123

2

61

2

2

2

2

2

30

15

0

7

1

1

3

1

1

0

(123)_{10} = (1111011)_2

Example (209.45)_{10} = (?)_2

2

209

Remainder

2

104

1

2

52

0

2

26

0

2

13

0

2

6

1

2

3

0

2

1

1

2

0

1

.45*2 =0.90 =

.90*2 = 1.80 =

.80*2 =1.60 =

.60*2 = 1.20 =

(209.45)_{10} = (11010001.0111)_2

Tabular Method

... 2048 1024 512 256 128 64 32 16 8 4 2 1

Example (123)_{10}=(?)_2

128 64 32 16 8 4 2 1

0 1 1 1 1 0 1 1

(123)_{10} = (1111011)_2

Example (17)<sub>10</sub>=(?)<sub>2</sub>

16 8 4 2 1

1 0 0 0 1

(17)_{10} = (10001)_2

Example (27)_{10}=(?)_2

16 8 4 2 1

1 1 0 1 1

(27)_{10} = (11011)_2

Example (81)_{10}=(?)_2

64 32 16 8 4 2 1

```

```

Example (13)_{10} = (?)_2

8 4 2 1

1 1 0 1

(13)_{10} = (1101)_2

Example (9)_{10}=(?)_2

8 4 2 1

1 0 0 1

(9)_{10}=(1001)_2

Example (2)_{10}=(?)_2

2 1

1 0

(2)_{10}=(10)_2

Binary To Decimal:-

Example:- (1111011)<sub>2</sub>=(?)<sub>10</sub>

1*2^6+1*2^5+1*2^4+1*2^3+0*2^2+1*2^1+1*2^0

64 + 32 + 16 + 8 + 0 + 2 + 1

(123)_{10}

=

Binary To Decimal:-

Example:- (1111011.101)<sub>2</sub>=(?)<sub>10</sub>

1 * 2^{6} + 1 * 2^{5} + 1 * 2^{4} + 1 * 2^{3} + 0 * 2^{2} + 1 * 2^{1} + 1 * 2^{0} + 1 * 2^{-1} + 0 * 2^{-2} + 1 * 2^{-3}

64 + 32 + 16 + 8 + 0 + 2 + 1 + .5

+0 + .125

=

(123.625)_{10}

Binary To Decimal(Using Tabular Method):-

Example: (1111011)_2 = (?)_{10}

64 32 16 8 4 2 1

1 1 1 1 0 1 1

64+32+16+8+0+2+1=(123)_{10}

Binary Arithmetic Operations:-

✓ Addition.(+)

✓ Subtraction.( -)

✓ Multiplication.(*)

✓ Division.(/)

Addition:-

Example:-1

...16 8 4 2 1

111101

+1111111

11111100

Carry=

Example:-2

111101

111101

+ 1111111

Carry=101

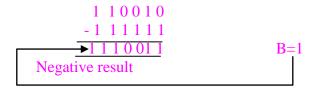

Subtraction/Minus:-

0-0 = 0

Borrow=0

```

1-0

1

Borrow=0

## Example1:-

## Example2:-

## **Multiplication:**

$$\begin{array}{r}

111.11 \\

& *111 \\

111111 \\

111111

\end{array}$$

$$110110.01$$

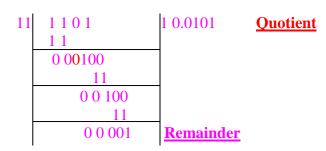

## **Division:**-

$$(1101)_2/(11)_2=(?)_2$$

## **Decimal to Octal:-**

Example

$$(123)_{10} = (?)_8$$

8 | 123 | Remainder

$$\blacktriangle$$

| 15 | 3 | 1 | 7 | 0 | 1

$$=(123)_{10}=(173)_8$$

## Example $(503)_{10}=(?)_{16}$

| 16 | 503 | Remainder A |

|----|-----|-------------|

| 16 | 31  | 7           |

| 16 | 1   | 15=F        |

| 16 | 0   | 1           |

|    |     | I .         |

$$=(1F7)_{16}$$

```

Example (523.45)_{10} = (?)_{16}

16<sub>1</sub>

523<sub>1</sub>

Remainder A

16

32

11=B

16

2

0

0

2

16

.45*16 = 7.20 = 7

.2*16 = 3.2

.2*16 =3.2

=(20B.733)_{16}

HexaDecimal To Decimal:

(1F7)_{16}=(?)_{10}

=1*16^2+F*16^1+7*16^0

=256+15*16+7

=256+240+7

=256+247

=(503)_{10}

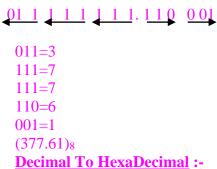

Binary to HexaDecimal:-

(1111111111.110001)_2

<u>1 1 1 1 1 1 1 1 1 1 . 110 0 0100</u>

1 1 1 1=15=F

1 1 1 1=15=F

1 1 0 0=12=C

0 1 0 0=4

(FF.C4)<sub>16</sub>

Compliments:-

1's Compliment.

2's Compliment.

Example:-1

1's Compliment=

(10001)_2 ———

→01110

1's compliment

Example:-2

2's Compliment=1's Compliment +1

(10001)_2 \longrightarrow 01110 +1=01111

1's compliment

2's compliment

Sign Magnitude:-

+

0

1

Example:-

1's

2's

(-17)_{10} \longrightarrow +17 \longrightarrow 010001 \longrightarrow 101110 \longrightarrow 101110+1=101111

```

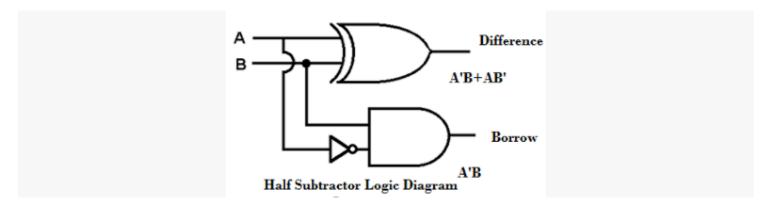

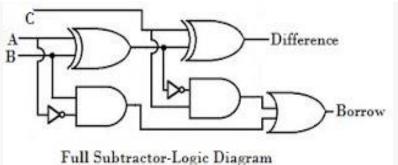

## **Logic Gates:-**

It is used for making/Designing digital circuit. There are many types of gates.

- ✓ AND Gate.

- ✓ OR Gate.

- ✓ NOT Gate.

- ✓ NAND Gate.

- ✓ NOR Gate.

- ✓ EX-OR Gate.

- ✓ EX-NOR Gate.

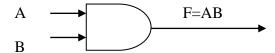

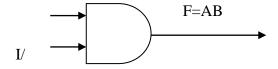

#### **AND GATE:-**

## **TRUTH TABLE:-**

Let n=input variable

Input Signal=2<sup>n</sup>

$$n=2(A, B) = 2^2=4(0, 1, 2, 3)$$

| A | В | F=AB |

|---|---|------|

| 0 | 0 | 0    |

| 0 | 1 | 0    |

| 1 | 0 | 0    |

| 1 | 1 | 1    |

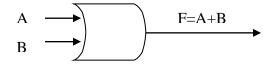

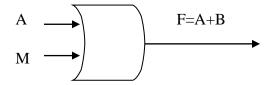

#### **OR GATE:-**

## **TRUTH TABLE:-**

Let n=input variable

Input variable=2<sup>n</sup>

$$n=2(A, B) = 2^2=4(0, 1, 2, 3)$$

|   |   | S 2 2 2 |

|---|---|---------|

| A | В | F=A+B   |

| 0 | 0 | 0       |

| 0 | 1 | 1       |

| 1 | 0 | 1       |

| 1 | 1 | 1       |

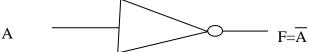

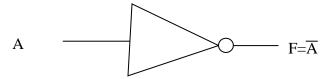

## **NOT GATE:-**

## **TRUTH TABLE:-**

Let n=input variable

Input variable=2<sup>n</sup>

$$n=1(A)=2^1=2(0,1)$$

A

$$F=\overline{A}$$

0

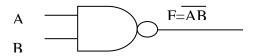

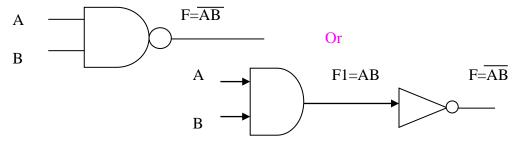

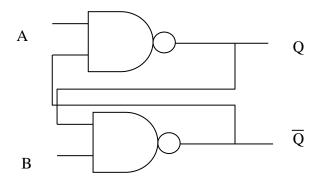

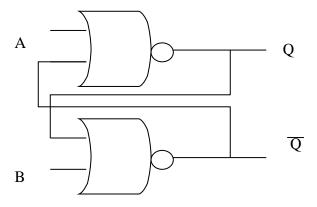

## **NAND/NOT-AND GATE:-**

## **TRUTH TABLE:-**

Let n=input variable

Input variable=2<sup>n</sup>

$$n=2(A, B) = 2^2=4(0, 1, 2, 3)$$

A

B

F1=AB

F=AB

0

0

1

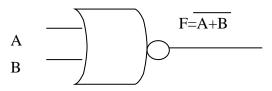

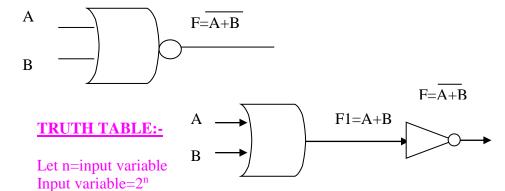

## **NOR GATE:**

## **TRUTH TABLE:-**

Let n=input variable

Input variable=2<sup>n</sup>

$$n=2(A, B) = 2^2=4(0, 1, 2, 3)$$

| A | В | F1=A+B | F=A+B |

|---|---|--------|-------|

| 0 | 0 | 0      | 1     |

| 0 | 1 | 1      | 0     |

| 1 | 0 | 1      | 0     |

| 1 | 1 | 1      | 0     |

## **EX-OR GATE:-**

$$\begin{array}{c|c}

A & \longrightarrow \\

B & \longrightarrow \\

\end{array}$$

## **TRUTH TABLE:-**

Let n=input variable

Input variable=2<sup>n</sup>

$$n=2(A, B) = 2^2=4(0, 1, 2, 3)$$

| Α | B | $\overline{\mathbf{A}}$ | $\overline{\mathbf{B}}$ | $\overline{A}B$ | $A\overline{B}$ | $\overline{A}B+A\overline{B}$ |

|---|---|-------------------------|-------------------------|-----------------|-----------------|-------------------------------|

|   | 0 |                         |                         |                 |                 |                               |

| 0 | 1 | 1                       | 0                       | 1               | 0               | 1                             |

| 1 | 0 | 0                       | 1                       | 0               | 1               | 1                             |

| 1 | 1 | 0                       | 0                       | 0               | 0               | 0                             |

## **EX-NOR GATE:-**

## **TRUTH TABLE:-**

Let n=input variable

Input variable=2<sup>n</sup>

| n=2( | (A,B)= | $2^2 = 4(0, 1)$         | 1,2,3)                  |                                   |                          |                               |                               |

|------|--------|-------------------------|-------------------------|-----------------------------------|--------------------------|-------------------------------|-------------------------------|

| A    | В      | $\overline{\mathbf{A}}$ | $\overline{\mathrm{B}}$ | $\overline{\mathbf{A}}\mathbf{B}$ | $A\overline{\mathrm{B}}$ | $\overline{A}B+A\overline{B}$ | $\overline{A}B+A\overline{B}$ |

| 0    | 0      | 1                       | 1                       | 0                                 | 0                        | 0                             | 1                             |

| 0    | 1      | 1                       | 0                       | 1                                 | 0                        | 1                             | 0                             |

| 1    | 0      | 0                       | 1                       | 0                                 | 1                        | 1                             | 0                             |

| 1    | 1      | 0                       | 0                       | 0                                 | 0                        | 0                             | 1                             |

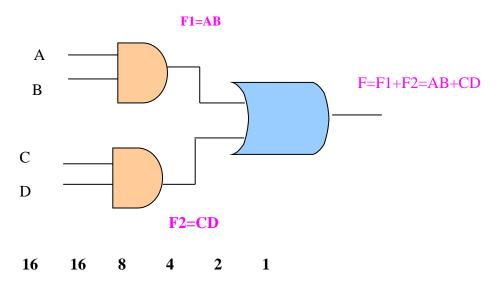

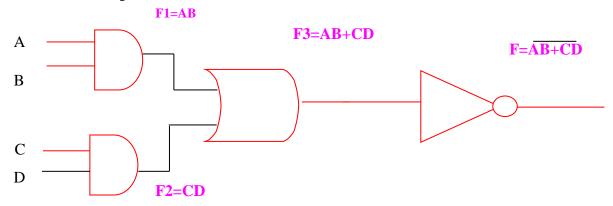

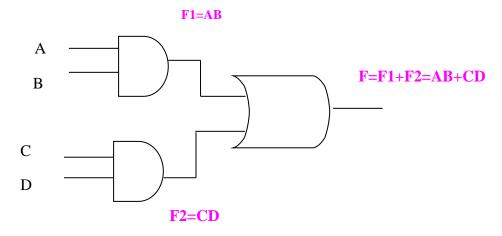

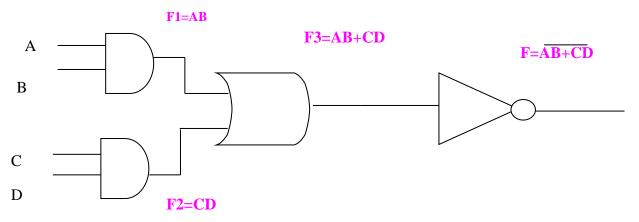

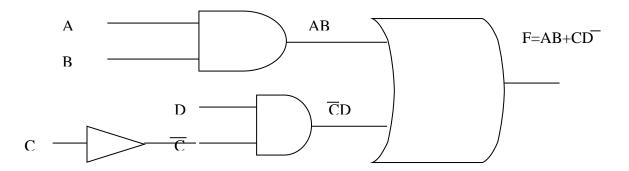

## **Combinational Circuit:-**

F=AB+CD is a Boolean Expression Where A, B, C, D are called Boolean variables.

## **Truth Table**

| A | В | C | D | AB | CD | AB+CD |

|---|---|---|---|----|----|-------|

| 0 | 0 | 0 | 0 | 0  | 0  | 0     |

| 0 | 0 | 0 | 1 | 0  | 0  | 0     |

| 0 | 0 | 1 | 0 | 0  | 0  | 0     |

| 0 | 0 | 1 | 1 | 0  | 1  | 1     |

| 0 | 1 | 0 | 0 | 0  | 0  | 0     |

| 0 | 1 | 0 | 1 | 0  | 0  | 0     |

| 0 | 1 | 1 | 0 | 0  | 0  | 0     |

| 0 | 1 | 1 | 1 | 0  | 1  | 1     |

| 1 | 0 | 0 | 0 | 0  | 0  | 0     |

| 1 | 0 | 0 | 1 | 0  | 0  | 0     |

| 1 | 0 | 1 | 0 | 0  | 0  | 0     |

| 1 | 0 | 1 | 1 | 0  | 1  | 1     |

| 1 | 1 | 0 | 0 | 1  | 0  | 1     |

| 1 | 1 | 0 | 1 | 1  | 0  | 1     |

| 1 | 1 | 1 | 0 | 1  | 0  | 1     |

| 1 | 1 | 1 | 1 | 1  | 1  | 1     |

Example 2 :-  $F=\overline{AB+CD}$

| A | В | C | D | AB | CD | AB+CD | AB+CD |

|---|---|---|---|----|----|-------|-------|

| 0 | 0 | 0 | 0 | 0  | 0  | 0     | 1     |

| 0 | 0 | 0 | 1 | 0  | 0  | 0     | 1     |

| 0 | 0 | 1 | 0 | 0  | 0  | 0     | 1     |

| 0 | 0 | 1 | 1 | 0  | 1  | 1     | 0     |

| 0 | 1 | 0 | 0 | 0  | 0  | 0     | 1     |

| 0 | 1 | 0 | 1 | 0  | 0  | 0     | 1     |

| 0 | 1 | 1 | 0 | 0  | 0  | 0     | 1     |

| 0 | 1 | 1 | 1 | 0  | 1  | 1     | 0     |

| 1 | 0 | 0 | 0 | 0  | 0  | 0     | 1     |

| 1 | 0 | 0 | 1 | 0  | 0  | 0     | 1     |

| 1 | 0 | 1 | 0 | 0  | 0  | 0     | 1     |

| 1 | 0 | 1 | 1 | 0  | 1  | 1     | 0     |

| 1 | 1 | 0 | 0 | 1  | 0  | 1     | 0     |

| 1 | 1 | 0 | 1 | 1  | 0  | 1     | 0     |

| 1 | 1 | 1 | 0 | 1  | 0  | 1     | 0     |

| 1 | 1 | 1 | 1 | 1  | 1  | 1     | 0     |

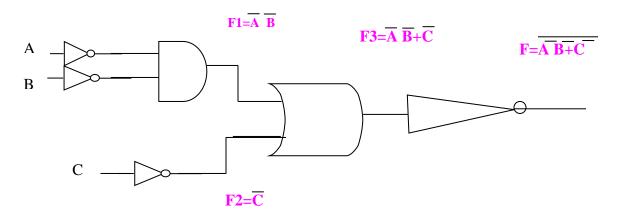

Example 3:-  $F = \overline{A} \overline{B} + \overline{C}$  Design circuit and truth table.

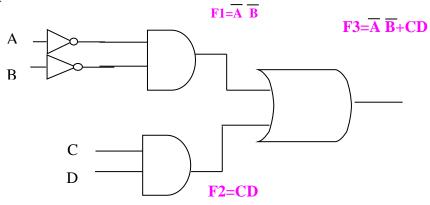

## Example 4:- $F=\overline{A}\overline{B}+CD$

| A | В | С | D | Ā | В | <del>A</del> <del>B</del> | CD | $\overline{\mathbf{A}} \ \overline{\mathbf{B}} + \mathbf{C}\mathbf{D}$ |

|---|---|---|---|---|---|---------------------------|----|------------------------------------------------------------------------|

| 0 | 0 | 0 | 0 | 1 | 1 | 1                         | 0  | 1                                                                      |

| 0 | 0 | 0 | 1 | 1 | 1 | 1                         | 0  | 1                                                                      |

| 0 | 0 | 1 | 0 | 1 | 1 | 1                         | 0  | 1                                                                      |

| 0 | 0 | 1 | 1 | 1 | 1 | 1                         | 1  | 1                                                                      |

| 0 | 1 | 0 | 0 | 1 | 0 | 0                         | 0  | 0                                                                      |

| 0 | 1 | 0 | 1 | 1 | 0 | 0                         | 0  | 0                                                                      |

| 0 | 1 | 1 | 0 | 1 | 0 | 0                         | 0  | 0                                                                      |

| 0 | 1 | 1 | 1 | 1 | 0 | 0                         | 1  | 1                                                                      |

| 1 | 0 | 0 | 0 | 0 | 1 | 0                         | 0  | 0                                                                      |

| 1 | 0 | 0 | 1 | 0 | 1 | 0                         | 0  | 0                                                                      |

| 1 | 0 | 1 | 0 | 0 | 1 | 0                         | 0  | 0                                                                      |

| 1 | 0 | 1 | 1 | 0 | 1 | 0                         | 1  | 1                                                                      |

| 1 | 1 | 0 | 0 | 0 | 0 | 0                         | 0  | 0                                                                      |

| 1 | 1 | 0 | 1 | 0 | 0 | 0                         | 0  | 0                                                                      |

| 1 | 1 | 1 | 0 | 0 | 0 | 0                         | 0  | 0                                                                      |

| 1 | 1 | 1 | 1 | 0 | 0 | 0                         | 1  | 1                                                                      |

## Boolean algebra:-

## **Simplification Method of Boolean functions:**

- ✓ Algebraic method.

- ✓ Karnaugh maps (K-Map)

- ✓ Quine McClusky Method

### Algebraic method.

Theorem based on algebraic method:-

✓ Commutative law

$$A+B=B+A$$

$$A.B=B.A$$

✓ Associative law

$$A+(B+C)=(A+B)+C$$

$$A.(B.C)=(A.B).C$$

✓ Distributive law

$$A+(B.C)=(A+B).(A+C)$$

$$A.(B+C)=(A.B)+(A.C)$$

✓ Absorption Law

$$A+AB=A$$

✓ Identity law

$$A+0=A$$

$A.1=A$

✓ Inverse law

$A\bar{A}=0$

$A+\bar{A}=1$

✓ Demorgan's law

$A+\bar{B}=\bar{A}\;\bar{B}$

$A\bar{B}=\bar{A}+\bar{B}$

✓ Double compliment

# A=A Simplify the Following Boolean functions:-

Question 1:- A+1=1

Solution:-

$$A+A+\bar{A}$$

$$=(A+A)+\bar{A}$$

$$=A+\bar{A}$$

$$=1$$

Question 2:-

$$\overline{(\overline{\overline{A}} + \overline{\overline{B}})} + (\overline{\overline{A} + \overline{\overline{B}}})$$

Solution:-

$$= \overline{(\overline{A} + \overline{B})}.(\overline{A} + \overline{\overline{B}}) \text{ {By Using demargons law}}$$

$$= (\overline{A} + \overline{B}).(A + \overline{B}) \text{ {By Using double compliment method}}$$

$$= \overline{A} A + \overline{A} \overline{B} + \overline{B} A + \overline{B} \overline{B}$$

$$= 0 + \overline{B}(\overline{A} + A) + \overline{B}$$

$$= 0 + \overline{B} + \overline{B}$$

$$= \overline{B}$$

Home Work:-

- 1. A \* A = A

- 2. Simplify the Boolean expression (A+B+C)(D+E)' + (A+B+C)(D+E)

- 3. Simplify the Boolean property x + x'y = x + y

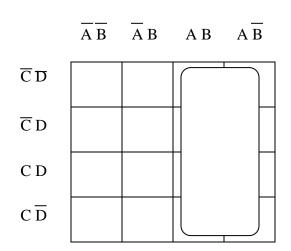

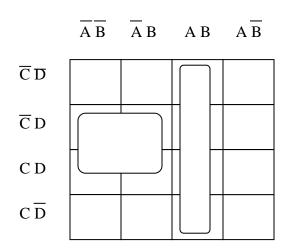

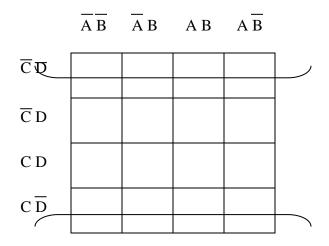

## Karnaugh maps (K-Map):-

## Karnaugh maps (K-Map):-

A Karnaugh map (K-map) is a pictorial method used to minimize Boolean expressions without having to use Boolean algebra theorems and equation manipulations. A K-map can be thought of as a special version of a truth table . Using a K-map, expressions with two to four variables are easily minimized.

## **Canonical and Standard Forms:**

$\checkmark$  SOP(Sum of product) Σ It is called Minterm or Standard Sum  $\checkmark$  POS(product of Sum) ∏ It is called Maxterm or standard Product

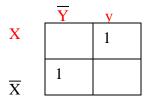

## $\Sigma$ SOP (Sum of product) For Two Boolean variables:-

| A | В | Σ                                              | Term           |

|---|---|------------------------------------------------|----------------|

| 0 | 0 | $\overline{\mathbf{A}}  \overline{\mathbf{B}}$ | $\mathbf{M}_0$ |

| 0 | 1 | <del>A</del> B                                 | $\mathbf{M}_1$ |

| 1 | 0 | $A\overline{B}$                                | $\mathbf{M}_2$ |

| 1 | 1 | AB                                             | $M_3$          |

## **∏ POS(product of Sum):-**

| A | В | П                                               | Term           |

|---|---|-------------------------------------------------|----------------|

| 0 | 0 | A+B                                             | $\mathbf{M_0}$ |

| 0 | 1 | $A+\overline{B}$                                | $\mathbf{M_1}$ |

| 1 | 0 | $\overline{\mathbf{A}}$ + $\mathbf{B}$          | $\mathbf{M}_2$ |

| 1 | 1 | $\overline{\mathbf{A}} + \overline{\mathbf{B}}$ | M <sub>3</sub> |

Example 1  $F = \Pi(0,1,2,3,4,8,12)$  Example 2  $F = \Pi(0,1,2,3,4,9,19)$

## $\Sigma$ SOP (Sum of product) For Three Boolean variables:-

| A | В | С | Σ                                                                 | Term             |

|---|---|---|-------------------------------------------------------------------|------------------|

| 0 | 0 | 0 | $\overline{\mathbf{A}}\overline{\mathbf{B}}\overline{\mathbf{C}}$ | $\mathbf{M}_{0}$ |

| 0 | 0 | 1 | $\overline{\mathbf{A}}  \overline{\mathbf{B}}  \mathbf{C}$        | $M_1$            |

| 0 | 1 | 0 | ABC                                                               | $M_2$            |

| 0 | 1 | 1 | ABC                                                               | M <sub>3</sub>   |

| 1 | 0 | 0 | A B C                                                             | M <sub>4</sub>   |

| 1 | 0 | 1 | A B C                                                             | M <sub>5</sub>   |

| 1 | 1 | 0 | AB C                                                              | M <sub>6</sub>   |

| 1 | 1 | 1 | A B C                                                             | M <sub>7</sub>   |

| POS (Product of Sum) For Three Boolean variables:-

| A | В | C | П                                                                       | Term           |

|---|---|---|-------------------------------------------------------------------------|----------------|

| 0 | 0 | 0 | A+B+C                                                                   | $\mathbf{M}_0$ |

| 0 | 0 | 1 | $A + B + \overline{C}$                                                  | $\mathbf{M}_1$ |

| 0 | 1 | 0 | $A + \overline{B} + C$                                                  | $M_2$          |

| 0 | 1 | 1 | $A + \overline{B} + \overline{C}$                                       | $M_3$          |

| 1 | 0 | 0 | $\overline{\mathbf{A}} + \mathbf{B} + \mathbf{C}$                       | $\mathbf{M_4}$ |

| 1 | 0 | 1 | $\overline{\mathbf{A}} + \mathbf{B} + \overline{\mathbf{C}}$            | $M_5$          |

| 1 | 1 | 0 | $\overline{\mathbf{A}} + \overline{\mathbf{B}} + \mathbf{C}$            | $M_6$          |

| 1 | 1 | 1 | $\overline{\mathbf{A}} + \overline{\mathbf{B}} + \overline{\mathbf{C}}$ | M <sub>7</sub> |

## **Question:-**

Make a table for min term and max term of following Boolean functions and also simplify these.

F=

$$\Sigma$$

(0, 1, 5, 8, 9, 12)

F= $\prod$  (0, 1, 5, 8, 10, 14)

## For Min term $\Sigma$

|                |               | A      | В | C | D |

|----------------|---------------|--------|---|---|---|

| $M_0$          | =             | 0      | 0 | 0 | 0 |

| $\mathbf{M_1}$ | =             | 0      | 0 | 0 | 1 |

| $M_5$          | =             | 0      | 1 | 0 | 1 |

| $M_8$          | =             | 1      | 0 | 0 | 0 |

| <b>M</b> 9     | =             | 1      | 0 | 0 | 1 |

| $M_{12}$       | =             | 1      | 1 | 0 | 0 |

| For N          | <b>Iax</b> te | rm ∏:- |   |   |   |

|                |               | A      | B | C | D |

| $M_0$          | =             | 0      | 0 | 0 | 0 |

| $\mathbf{M_1}$ | =             | 0      | 0 | 0 | 1 |

| $M_5$          | =             | 0      | 1 | 0 | 1 |

| $M_8$          | =             | 1      | 0 | 0 | 0 |

| $M_{10}$       | =             | 1      | 0 | 1 | 0 |

| $M_{14}$       | =             | 1      | 1 | 1 | 0 |

#### Minimization of Gates By Using K-MAP:-

Table for Two Variables (Say A and B):-

|                | Ā | A |

|----------------|---|---|

| $\overline{B}$ | 0 | 1 |

| В              | 2 | 3 |

#### Parity bits:-

It is an additional bits, Which is used for finding and correcting errors in system. There are two types of parity bits.

- ✓ Odd parity bit

- ✓ Even parity bit

#### Example:-

Find out odd and even parity bit of following numbers.

$(1000101)_2$

Solution:-

Odd parity bits of 1=0

Even parity bits of 1=1

Odd parity bits of 0=1

Even parity bits of 0=0

#### Example:-

Find out odd and even parity bit of following numbers.

$(00001)_2$

#### Solution:-

Odd parity bits of 1=0

Even parity bits of 1=1

Odd parity bits of 0= 1

Even parity bits of 0=0

**Coding System:-**

There are following coding system uses in computer.

$\rightarrow$  (Binary Coded Decimal)

EBCDIC → (Extended Binary Coded Decimal Interchange Code)

ASCII → (American Standard Code for Information Interchange)

#### **BCD(Binary Coded Decimal):-**

It is four bits of coding system. It is also known as 8-4-2-1.

| d1 | d2 | d3 | d4 |

|----|----|----|----|

|    |    |    |    |

Weight of  $d1=2^3=8$ .

Weight of  $d2=2^2=4$ .

Weight of  $d3=2^1=2$ .

Weight of  $d4=2^0=1$ .

One nibble=  $\frac{1}{2}$  of a byte.

#### **EBCDIC** (Extended Binary Coded Decimal Interchange):-

It is eight bits of coding system, which is used in only mainframe computer system.

|  |  | d1 | d2 | d3 | d4 | d5 | d6 | d7 | d8 |

|--|--|----|----|----|----|----|----|----|----|

|--|--|----|----|----|----|----|----|----|----|

#### **ASCII (American Standard Code For Information Interchange)**

(Or Alpha Numeric Codes)

It is also eight bits of coding system. It is used in microcomputer system.

Its value exist between 0 to 255. There are two categories of ASCII codes.

a:-Standard ASCII codes (0-127)

> Non Printing ASCII Codes 0-31

Printing ASCII Codes 32-127 128-255

b:-Extended ASCII codes

It is used for making symbols.

Example:-

65-90 A-Z 97-122 a-z

Alt+ASCII codes (Numeric Key Pads)

#### **History of Computer:-**

#### **History of Computer:-**

Computer developed before 300BC at China. This computing device was known as abacus.

- Mechanical Computer.

- Electromechanical computer.

- Electronic Computer.

#### **Mechanical Computer:-**

It was very first attempt towards automatic computing device. Blaise Pascal designed a mechanical computer that was known as Pascaline. It consist of a lot of gears and chains. It can perform repeated addition and subtraction. After some time the grand father (Charles Babbage) of modern computer also designed following two mechanical computer.

- Difference Engine.

- ❖ Analytical engine by Babbage.

Above both kinds of mechanical computer can perform repeated addition, subtraction, multiply, division, solving polynomial equation and trigonometric problems.

Blaise Pascal→Date of Birth 19 June 1623→ France Date of Died 19 August 1662→Paris Charles Babbage → Date of Birth 26 Dec 1791→ London 18 October1871→London Date of Died

#### Electromechanical computer.

It was the next attempt towards automatic electronic apparatus that was afforded by Howard Aiken at Harvard University. He designed first electromechanical computer that was known as MARK-I. It was sponsored by IBM and UN Navy.

Date of Birth 8 March 1900 → Hoboken New Jersey Died 14 March 1973

### **Electronic computer:-**

#### Generation:-

- First generation (1942 to 1955).

- **❖** Second Generation → (1955 to 1964).

- $\diamond$  Third Generation  $\rightarrow$ (1964 to 1975).

- (1975 to 1990).  $\bullet$  Fourth Generation  $\rightarrow$

- $\bullet$  Fifth generation  $\rightarrow$ (yet to come).

#### First generation:-

In this generation vacuum tube was used in processor technology. There are many types of vacuum tubes.

- Diode(Cathode & Anode Plate)

- o Triode(Cathode, Anode Plate & Suppressor Grid).

- o Tetrode(Four plates).

- o Pentode(Five plates).

Using vacuum tubes following types of electronic computers was designed.

- **ENIAC** (Electronic Numerical Integrator and calculator).

- **EDVAC** (Electronic Discrete Variable automatic Computer).

- **UNIVAC** (Universal Automatic Computer).

## **Characteristics of ENIAC:-**

- It was Very Giant Machine.

- **!** Its weight was 30 tones.

- ❖ It may perform 5000 addition or 500 multiplications per minute.

- It occupies a number of rooms.

- ❖ It needed a lot of electricity.

- **!** It needed a lot of cooling requirements.

- ❖ It emitted a lot of heat.

- ❖ Portability is very complex task.

- \* There were 18000 vacuum tubes were used.

#### **Second generation:-**

In this generation vacuum tube was replaced by <u>transistor</u>. By using transistor IBM (International business Machine) designed <u>IBM 700</u> series of processors. It consumes less electricity and cooling requirement system. Its speed was faster than first generation computer.

#### **Example of transistor:-**

n-p-np-n-pn-pTransistor.n-pTransistor.p-nTransistor.

Transistor based processor much faster than vaccum-based processor.

## Third generation:-

In this generation, integration technology known as <u>IC</u> (Integrated Circuit) was used. It consists of a lot of transistor, capacitor and other electronics components.

#### IC Technology:-

| SSI         | (Small Scale Integrator).                           |  |  |  |

|-------------|-----------------------------------------------------|--|--|--|

| MSI         | (Medium Scale Integrator).                          |  |  |  |

| LSI         | (Large Scale Integrator).                           |  |  |  |

| VLSI        | (Very Large Scale Integrator).                      |  |  |  |

| ULSI        | (Ultra Large Scale Integrator).                     |  |  |  |

|             |                                                     |  |  |  |

| <u>SSI</u>  | Number of gates below 100.                          |  |  |  |

| <u>MSI</u>  | Number of gates upto 100 or more.                   |  |  |  |

| <u>LSI</u>  | Number of gates upto 1000.                          |  |  |  |

| <u>VLSI</u> | Number of gates upto 10 <sup>6</sup> (Chips).       |  |  |  |

| ULSI        | Number of gates upto 10 <sup>8</sup> (Micro Chips). |  |  |  |

#### Fourth generation:-

In this generation, <u>VLSI</u> based technology used in processor (CPU) used.

#### Feature:-

- ❖ Smaller.

- Faster.

- ❖ GUI (Graphic User Interface).

#### Fifth generation:-

In this generation, <u>ULSI</u> based technology used in processor used.

#### Example:-

- \* ROBOT.

- Fighter Plane.

- ❖ Shuttle Space Plane (Its speed=40000KM/Hour).

Etc.

Intel Company designed first microprocessor 4004 in 1971 .It was specific purpose processor. Intel Company designed second microprocessor 8088 in 1974 .It was general purpose processor.

## Classification of computer(Digital Computer):-

- Micro computer.

- Minicomputer.

- Mainframe Computer.

- Super Computer.

#### **Micro Computer:-**

It is small computer, which is used for personal work.

#### Example:-

- **❖** PC

- Laptop

- **\*** Tablet

- Palmtop

etc.

#### Mini Computer:-

It is larger than microcomputer which is used for small networking purpose.

#### **Mainframe Computer:-**

It is also used for networking purpose. It is suited for big organization.

#### Example:-

MEDHA

**DEC**

SPERRY etc.

## Super Computer:-

It is the fastest computing device, which is used for solving complex problems.

#### Example:-

**PARAM**

**CORAY**

**INDIGINIOUS**

Etc.

#### **Application of Super Computer:-**

- **❖** Airlines Controlling

- Weather forecasting

- Shuttle space controlling

- ❖ Medical Science

etc

#### **Types of Computer:-**

Analog Computer.

Digital Computer.

Hybrid Computer.

#### **Analog Computer.**

Such types of computers are used for measuring temperature, pressure, speed etc.

Example:-

Thermometer

Speedometer

Barometer

#### Digital Computer.

#### **Classification Digital Computer:-**

- Micro computer

- Minicomputer

- Mainframe Computer

- Super Computer

#### **Hybrid Computer:-**

32Such type of computers uses both categories of technology.

#### Example:-

- **&** ECG Machines.

- ❖ Nuclear control System.

- Hydrogenic System

## **Uses of Computer in Digital devices:-**

**❖** In Mobiles

- In Bank

- In Music

- In Robotic

#### Computer System:-

- Hardware

- o Input Devices (Ex:-Keyboard, Mouse, Joystick etc)

- o Processor(CPU)

- Output Devices(Ex Monitor,Speeker,Printer etc)

- Storage Devices(Ex Hard Disk,CD ROM,DVD ,Floppy Disk)

- Software

- System Software

- Operating System Example :-MS Windows XP,VISTA etc

- Application S/W Example :- MS word,MS excel,MS Power Point etc

- Development S/w Example:- C++,C#,Java,COBOL,PASCA,BASIC etc

#### Working of Computer System:-

#### **Process:-**

Running state of program is called process.

#### **Types of Processing:-**

There are two types of processing in computer system

- ❖ On line processing/Real Time processing(A device directly connected with CPU).

- ❖ Off Line Processing/Batch Processing(A device not directly connected with CPU).

## On line processing/Real Time processing:-

When processing takes place immediately as soon as the data is entered into the computer .It is called on line processing.

#### Off Line Processing/Batch Processing:-

When processing takes place on the stored data to get an output it is called **off line processing. Example:-** Data Stored and processed later stage.

Assignment of BCA-01 Question 1

Processing speed and performance determine by using technique of OR.

Block diagram of Processor:-

CPU may consist of ALU,CU and OR.

#### Feature of IBM 1401 PC:-

- ✓ It was announced in late 1950.

- ✓ Memory capacity was 16000 characters

- ✓ MSI,LSI technology was used

- ✓ Processing speed measured in MIPS

#### **Technology of Integration:-**

- ✓ SSI

- ✓ MSI

- ✓ LSI

- ✓ VLSI

- ✓ ULSI

#### Feature of IBM PC AT:-

- ✓ It was announced in 1984.

- ✓ Memory capacity was 200 times more characters than IBM 1401.

- ✓ VLSI technology was used in this processor

- ✓ PC AT stand for personal computer advanced technology.

- ✓ Processing speed of PC At is more than IBM 1401 PC

- ✓ Size of operational register is more than IBM 1401 PC (Processing speed measured in MIPS)

- ✓ It is chips based processor.

Note:-Chips

Small components that contains a large amount of electronic circuitry. They are building blocks of A computer and perform various functions such as doing arithmetic ,serving as computer memory or controlling other chips.

#### **Generation of Processor:-**

First Generation.

Second generation.

Third Generation.

Fourth Generation.

Fifth generation.

### Memory System in Computer/Memory Hierarchy in Computer:-

It is used for storing instructions and data permanently or temporarly for further use. It may also store audio, video, images, graphics, s/w etc.

Memory in a computer system is required for storage and subsequent retrieval of the instructions and data.

#### Example:-

Hard Disk/Electromagnetic Disk. CD ROM (Optical Memory). DVD (Optical Memory).

BLU Ray Disk (Optical Memory). Audio/Video Cassette (Magnetic tape)

Pen Drive/Flash Memory. Zip Disk.

Flopy Disk (Magnetic Disk). Memory Chips. RAM, ROM Etc.

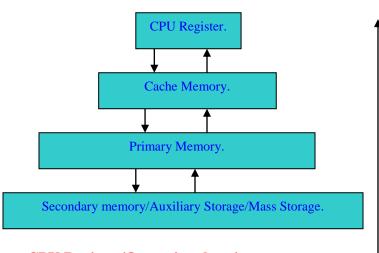

#### **Memory Hierarchy:-**

- 1:-Decreasing Size.

- 2:-Increasing Speed.

- 3:-Increasing Cost.

#### **CPU Register/Operational register:-**

It is the fastest memory in speed and smallest in size. It is very costly. It determines processing speed of CPU.Its speed measured in MIPS.

- M Million

- I Instruction

- P Per

- S Second

Larger the size of register faster may be the speed of CPU.

**Example:** 32 bits register Size→Slower Speed.

64 bits register size→Relatively faster speed.

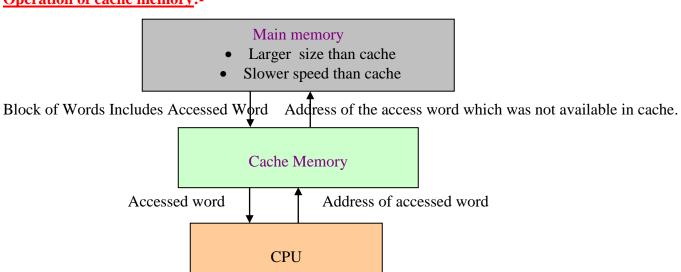

#### Cache memory/High Speed Memory:-

It is placed between CPU register and primary memory. It is used for increasing speed of CPU.

#### **Primary Memory/Main Memory:-**

It consists of semi conductor materials. Like Silicon(Si) and Germanium(Ge).

There are two types of primary memory.

- \* RAM(Random Access Memory).

- o SRAM(Static Random Access Memory).

- o DRAM(Dynamic Random Access Memory).

- **ROM**(Read Only Memory).

- o PROM (Programmable Read Only memory).

- o EPROM (Erasable PROM).

- o EEPROM (Electrically EPROM).

- o Flash Memory (Used in I/O storage device. Example I/O storage devices,MP3 music players, Digital camera) There are two kinds of flash memory

- Code storage flash:-It stores programming algorithms and largely found in cell phones

- Data Storage flash:-It stores data and comes digital cameras and MP3 players.

**Example:**-BIOS (Basic Input Output System)/Firmware.

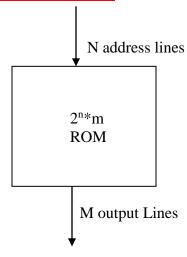

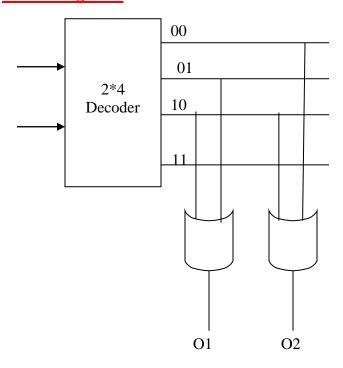

#### **Block Diagram of ROM:-**

| I <sub>1</sub> | $I_2$ | O <sub>1</sub> | $O_2$ |

|----------------|-------|----------------|-------|

| 0              | 0     | 0              | 1     |

| 0              | 1     | 1              | 0     |

| 1              | 0     | 1              | 1     |

| 1              | 1     | 0              | 0     |

Truth table of Simple ROM

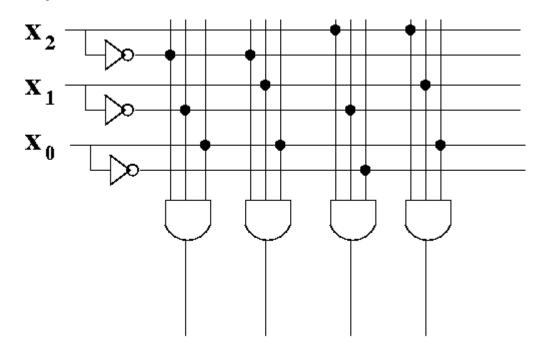

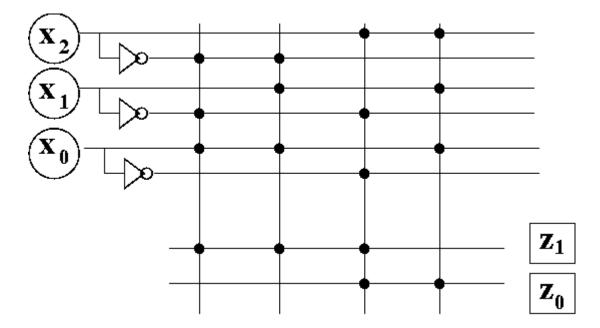

#### Circuit diagram:-

A ROM is essentially a memory or storage device in which a fixed set of binary information is stored. The number of distinct addresses possible with n input variables is  $2^n$ . A ROM is characterized by the number of words  $(2^n)$  and the number of bits(m) per word.

Example:-32\*8 ROM which can be written as 2<sup>5</sup>\*8 consist of 32 words of 8 bit each. It means there are 8 output lines and 32 distinct words stored in the unit.

**Difference Between RAM and ROM**

| RAM                                                  | ROM                       |

|------------------------------------------------------|---------------------------|

| Volatile Existence of data occur during running mode | Non Volatile(Permanently) |

| Uses by both users and System                        | Only for System           |

| Consist of Si And Ge                                 | Consist of Si And Ge      |

**Difference Between SRAM and DRAM**

| SRAM(Static Random Access Memory)                                         | DRAM(Dynamic Random Access Memory)                             |

|---------------------------------------------------------------------------|----------------------------------------------------------------|

| No loss of electrical Signal $(1 \leftrightarrow 1, 0 \leftrightarrow 0)$ | loss of electrical Signal $(1 \rightarrow 0, 0 \rightarrow 1)$ |

| No need of refreshment.                                                   | Need of refreshment.                                           |

| It is made with transistors.                                              | It is made with cells that stores data as charge               |

|                                                                           | capacitors.                                                    |

Difference between ROM, PROM, EPROM and EEPROM

| Name of Memory | Write Time   | Access Time                    | <u>Cycle</u> |

|----------------|--------------|--------------------------------|--------------|

| ROM            | Many Hours   | Nano Second(10 <sup>-9</sup> ) | 1            |

| PROM           | Less Hour    | Nano Second(10 <sup>-9</sup> ) | 10           |

| EPROM          | Minute       | Nano Second(10 <sup>-9</sup> ) | 100          |

| EEPROM         | Second       | Nano Second(10 <sup>-9</sup> ) | 1000         |

| Flash Memory   | Mili Seconds | Nano Second(10 <sup>-9</sup> ) | 10000        |

#### Secondary Memory/Auxiliary Memory/Backing Store:-

It is the largest storage device, which is used for storing data and information permanently.

#### Example:-

Hard Disk (Electro magnetic disk).

Pen Drive.

CD ROM (Optical Memory)/Compact Disk Read Only Memory.

DVD (Optical Memory)/Digital Video Disk/Digital Versatile Disk.

Blu Ray Disk (Optical Memory), CD-R.

CCD,Bubble Memories:-(They have arrays of cells that can hold charge packets of electron.A word is represented by a set of charge packets,the presence of each packets of represent the bit –value 1.

Audio/Video cassette (Magnetic tape).

Zip Drive.

Floppy Disk (Magnetic Disk).

Memory Chips (It uses technology of flash).

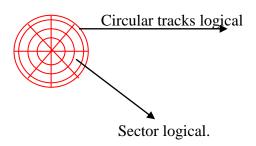

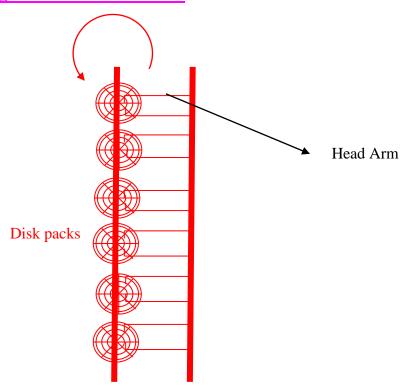

## Storage Mechanism In Magnetic Disk:-

In magnetic disk data stored in the form of logical circular tracks and sectors.

Circular Tracks and sectors. One Sector=512 Bytes.

### **Access Time:-**

Seek Time

Latency Time

For read and write, operation head is needed. There are two types of head

- Fixed head.

- **❖** Moveable head.

## **Seek Time:-**

Time required to position the head on a specific track for read and write operation is called **seek time**. **Latency Time:-**

The time required by a sector to reach below the read/write head is called **latency time**.

#### Storage Mechanism in hard disk:-

## **Access Speed Measurement Unit:-**

RPM (Rotation/Revolution Per Minute) is used for measuring speed.

RPM may be 3600, 7200, above 10000.

#### **Some Standard of Hard Disk**

40 GB Hard Disk 80 GB Hard Disk 120 GB Hard Disk 320 GB Hard Disk 560 GB Hard Disk 1 TB Hard Disk

Etc

#### Name of Company:-

Samsung, LG., Philips.Sony, Moser Bear, IBM (International Business Machine). Lenovo, Del, Segate, I-Ball, Compaq, HP, Apple, WD, Hitachi, Montec etc.

### Storage Mechanism in Optical memory(Spiral tracks & sectors are used for storage):-

- ❖ CD ROM(Compact Disk read Only Memory) Low density

- ❖ DVD(Digital Video Disk) High Density

- ❖ BLU RAY DISK Very Much High Density

- **❖** WORM(Write Once Read many)

#### **Read/Write Operations:-**

#### Laser beams are needed.

For CD ROM

For DVD

High Power of laser beams.

High Power of laser beams.

Very High Power of laser beams.

#### Data are stores in spiral tracks and sector type system/Organization.

Storage Capacity of CDROM (700 MB to 800 MB)

Storage Capacity of DVD (4 GB to 5 GB)

Storage Capacity of BLU Ray Disc (6 GB to 12 GB)

#### Storage Mechanism in Magnetic tape:-

#### **Access Method:-**

To retrieve (Read/Write operation) data from storage device by using following three technique.

- Sequential Access Method.

- Direct Access Method.

- Random Access Method.

#### **Sequential Access Method.**

To access data from storage system in sequential pattern. That is, One by One.

**Example:- Magnetic Tape.**

#### **Direct Access Method.**

To access data from storage device by using key value and corresponding address.

Example:-Magnetic disk,CD ROM.

#### **Random Access Method.**

To access data from storage device in random manner.

**Example:-Semiconductor Memories.**

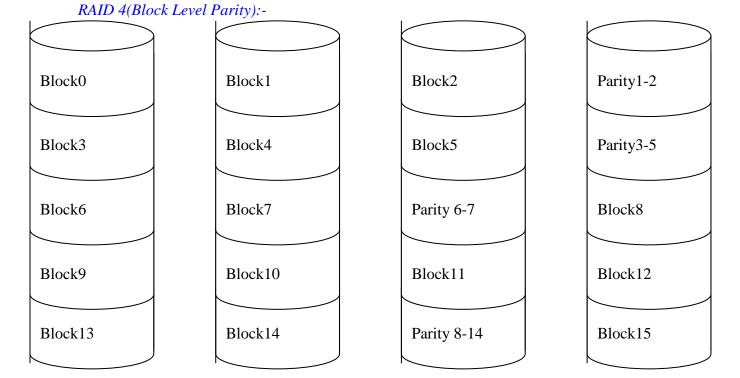

#### **RAID:-( Redundant Array of Independent Disks)**

It is a technology to improve the secondary storage media by increasing the capacity, performance and reliability. Multiple –disks database schemes, is termed as RAID.

Some of the basic questions for such systems are:

How are the disks organized?

Ans:-May be as an array of disks.

Can separate I/O requests be handled by such a system in parallel?

Ans:-Yes, but only if the disk accesses are from separate disks.

Can a single I/O requests be handled in parallel.

Ans:-Yes but the data block requested should be available on separate disks.

Can this array of disks be used for increasing reliability?

Ans:-Yes but for that redundancy of data is essential.

Characteristics of RAID disks:-

- OS considers the physical disks as a single logical drive.

- Data is distributed across the physical disks.

- In case of failure of a disk, the redundant information kept on redundant disks is used to recover the data.

| I                        | RAID 0(Non-Redu               | ındant)                                             |            | l                                          |        |                                                         |         |

|--------------------------|-------------------------------|-----------------------------------------------------|------------|--------------------------------------------|--------|---------------------------------------------------------|---------|

| Strip0                   |                               | Strip5                                              |            | Strip10                                    |        | Strip15                                                 |         |

| Strip1                   |                               | Strip6                                              |            | Strip11                                    |        | Strip16                                                 |         |

| Strip2                   |                               | Strip7                                              |            | Strip12                                    |        | Strip17                                                 |         |

| Strip3                   |                               | Strip8                                              |            | Strip13                                    |        | Strip18                                                 |         |

| Strip4                   |                               | Strip9                                              |            | Strip14                                    |        | Strip19                                                 |         |

|                          | RAID 1(Mirrored)              |                                                     |            |                                            |        |                                                         |         |

| Strip0                   | Strip5                        | Strip10                                             | Strip15    | Strip0                                     | Strip5 | Strip10                                                 | Strip15 |

| Strip1                   | Strip6                        | Strip11                                             | Strip16    | Strip1                                     | Strip6 | Strip11                                                 | Strip16 |

| Strip2                   | Strip7                        | Strip12                                             | Strip17    | Strip2                                     | Strip7 | Strip12                                                 | Strip17 |

| Strip3                   | Strip8                        | Strip13                                             | Strip18    | Strip3                                     | Strip8 | Strip13                                                 | Strip18 |

| Strip4                   | Strip9                        | Strip14                                             | Strip19    | Strip4                                     | Strip9 | Strip14                                                 | Strip19 |

| Strij b0 Strij Strij RAI | p1 p3 p4 ID 3( Bit Interleave | Strip5 Strip6 b1 Strip8 Strip9  ed Parity):- Block1 | ming Code) | Strip10 Strip11 b2 Strip13 Strip14  Block2 |        | Strip15 Strip16 Parity bit b Strip18 Strip19  Parity1-2 |         |

| Bloo                     | ck6                           | Block4 Block7                                       |            | Block5 Block8                              |        | Parity 6-8                                              |         |

| Bloo                     | ck12                          | Block10 Block13                                     |            | Block11 Block14                            |        | Parity 9-11 Parity12-14                                 |         |

RAID 5(Block Level Distributed Parity)

*RAID 6(Dual Redundancy)*

In RAID technologies have two important performance considerations

- The data transfer rate.

- Input/Output request rate.

High data transfer rate dependent on:

- Path between individual disks and memory.

- Fulfillment of an I/O request by multiple disks of array.

## **Concepts of High Speed memories:-**

There are four possible answers to increase speed of CPU.

- Decrease the memory access time.

- Access more words in single access cycle.

- Insert a high speed memory termed as cache memory between processor and main memory.

- Use associate addressing in place of random access.

#### **Operation of cache memory:-**

The use of cache memory requires several design issues to be addressed. Some of design issues are briefly summarized below.

- Cache Size:- Example:-64 KB, 128 KB, 512 KB or 1 MB.

- Block Size:-It refers to the unit of data exchanged between cache and main memory.

- Replacement policy:-When a new block is to be fetched into the cache, another may have to be replaced to make room for new block.

- Write policy:-The write policy decides when the altered words of a block are written back to main memory.

#### **Brief Description of Cache organization:-**

Cache memories are found in almost all latest computers. They are very useful for increasing the speed of access of information from main memory. The idea of cache memory is that by keeping the most frequently accessed instructions and data in the fast cache memory.

The performance of cache memory is frequently measured in terms of quantity called <u>hit ratio</u>.

If the word is not found in cache, it is in the main memory and it counts as a miss.

#### Mapping/Relationship procedure:-

Data from main memory to cache memory is referred to as a mapping process. There are three types of mapping organizations:-

- Associative Mapping/Relationship.

- Direct Mapping/Relationship.

- Set Associative mapping/Relationship.

#### **Associative Mapping:-**

This memory stores both the address and data of the memory word.

#### **Direct Mapping:-**

The direct mapping cache organization uses the n-bit address to access the main memory and k-bit index to access the cache.

#### **Set associative:-**

This mapping is improvement on direct mapping organization in that each word of cache can store two or more words of memory under the same index address.

#### **Chip Organization:-**

Chip consist of semiconductor material. In chip it is an arrangement of decoder, bit line and word line. There are several technique used for a chip. Following two common technique uses mostly in chip

- **2**D Chip organization.

- 2 ½ D Chip Organization.

Figure Page Number (a) and (b) page Number 92 and 93.

#### Differences between 2D and 2 ½ D

| <u>2D</u>                                                | 2 ½ D                                                |

|----------------------------------------------------------|------------------------------------------------------|

| It require more circuitry.                               | It require less circuitry.                           |

| Error detection and correction codes are not effectively | Error detection and correction codes are effectively |

| used.                                                    | used.                                                |

| 16 bits or 32 bits input/output pins are used.           | Only one I/O pin is used.                            |

Etc.

#### **Both Input/Output devices:-**

\* MODEM (Modulator & Demodulator).

It is used for internet connection.

- \* Touch Screen.

- Communication Port.

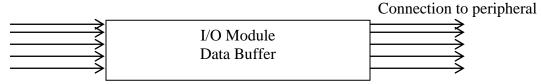

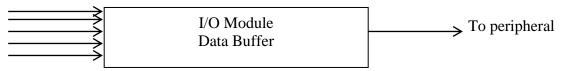

#### I/O Module:-

An I/O module is a mediator between the processor (CPU) and I/O devices.

#### **Function/Task Of Module:-**

- ❖ It should be able to provide control and timing signal.

- ❖ It should communicate with CPU.

- ❖ It should communicate with I/O devices.

#### Input/Output Technique:-

The I/O operations can be performed by three basic techniques. These techniques are:

- Programmed I/O

- ❖ Interrupt Driven I/O

- Direct Memory Access(DMA)

#### **Programmed I/O:-**

It is useful I/O method for computers where hardware costs need to be minimized. It perform following functions

- ❖ Transfer of data from I/O device to the CPU registers/OR.

- ❖ Transfer of data from CPU register/OR to Memory.

#### Interrupt (It is a program):-

It is a mechanism for transferring a <u>block of data from one memory</u> to <u>another memory</u>. It also performs following operations. The term interrupt is defined loosely to any exceptional event that cause CPU to temporarily transfer its control currently executing program to a different program which provide service to exceptional event.

- ❖ Initiation of I/O operation.

- Completion of I/O operation.

- ❖ Occurrence of H/W or S/W errors.

#### **Direct Memory Access (DMA):-**

It is a module for transfer large amount of data from CPU.DMA operate in the following way.

- \* Which operation to be performed.

- The address of I/O device which is to be used.

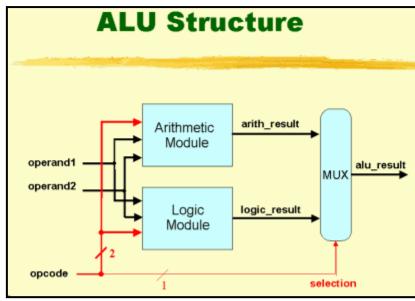

#### I/O Processors:-

#### It include following steps.

- Step 1:-Direct Control of CPU on I/O device.

- Step 2:- Introduction of I/O module.

- Step 3:-CPU need not wait for I/O operations to complete.

- Step 4:- Direct access of I/O module to the memory via DMA.

#### What Is scanners:-

It is an input device that allows we to capture drawing or photographs or text from tangible source (Paper, slides etc) into electronic form. There are various types of scanners.

- Drum scanners

- Hand scanners

- Video scanners

#### What Is SMPS:-

It converts AC current into DC current for computer. It is referred to as Switched Mode Power Supply.

AC (Alternative Current) → DC (Direct Current)

## Advantage of SMPS:-

- It generates less heat.

- It produces power range between 150 to 200 watts.

- It uses less expensive transformers and circuit.

#### What Is Modems:-

It is used for converting analog signal to digital signal and digital to analog signal.

It is used for internet connection.

There are many types of MODEMs.

- Internal Modems.

- External Modems.

- Pocket Modem.

- PC Card Modems.

Modem understand a set of instructions called Hayes command set or AT command Set.

## **Technology of LCD:-**

It is a technology for VDU.It consumes less electric power and produce less harmful radiation.Images are generated by crystal rods.

There are following three types of LCD technology.

- Marketive LCD (It is display generated by selectively blocking reflected light).

- Backlit LCD(It is display due to a light source behind LCD panel).

- Edgelit LCD (It is display due to a light source adjacent to the LCD panel).

## Mechanism of CRT screen:-

It is a major technology on which monitors and televisions have been based. Following factors influence the quality of image of the monitor.

- **1:-The phosphor coating:**-This effect the color and the persestitence (The period the effect of a single hit on a dot lasts).

- **2:-The Cathode (Electron Gun)**:-The sharpness of image depends on the good functioning of this gun.

- **3:-The Shadow Mask/Aperture Grill**:-This determines the resolution of the screen in color monitor.

- **4:-**The screen, glare and lighting of the monitor.

Bandwidth of CRT screen:- It is combination of address of each pixels and synchronization signal.

**DPI of CRT screen:** It is a measure for the actual measure for the actual sharpness of the onscreen image. This depends both resolution and size of the image.

Monitor resolution:-It depends upon video cards. There are two types of frequency generated by CRT.

A:- Horizontal Frequency.

B:- Vertical frequency.

Both types of frequency measured in KHz.

#### Color Depth:-

It is clear that an image consists of an array of pixels.

| Color Mode | Depth (Bits/pixel) |

|------------|--------------------|

| Monochrome | 1                  |

| 16 colors  | 4                  |

| 256 colors | 8                  |

| High color | 16                 |

| True Color | 24                 |

### **External Interfaces:-**

I/O module and the peripherals are characterized into two main categories:

- A: Parallel Interface.(It is used for connecting printer)

- B: Serial Interface.(It is used for connecting Mouse and MODEM)

#### Figure of Parallel Interface:-

Connection to system bus/wires or circuits

#### Figure of Serial Interface:-

Connection to system bus/ wires or circuits

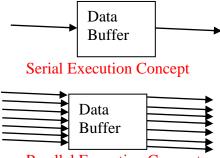

#### What is Parallel Processing:-

Parallel computer is classified by According to M.J. Flynn's. There are four categories of computer.

- ✓ SISD (Single Instruction Single data).

- ✓ SIMD (Single Instruction Multiple data).

- ✓ MISD (Multiple Instruction Single data).

- ✓ MIMD (Multiple Instruction Multiple data).

#### SISD:-

Using this technology, Single Instruction applies on single data stream through pipeline.

Example:-Conventional Von Neumann architecture.

#### SIMD:-

Using this technology, Single Instruction applies multiple data stream or Instructions broadcast on multiple data stream.

Example:-Array Processors.

#### MISD:-

Using this technology, Multiple Instruction applies on single data stream.

Example:-Distributed architecture, Vector Processors.

#### MIMD:-

Using this technology, Multiple Instruction applies on multiple data stream.

Example:-Multiprocessor System, Data Flow architecture.

#### **Multiprocessor Interconnections:-**

- Bus Oriented System.

- Crossbar Connected System.

- Hypercube.

- Multistage switched based system.

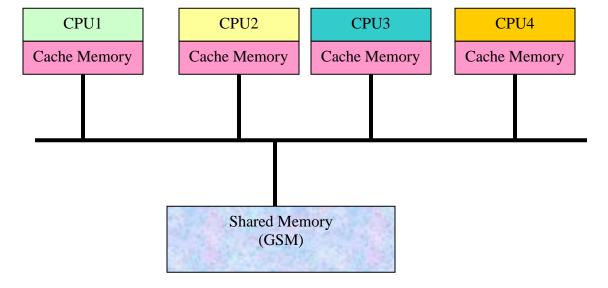

UMA (Uniformly Memory Access) tightly coupled system

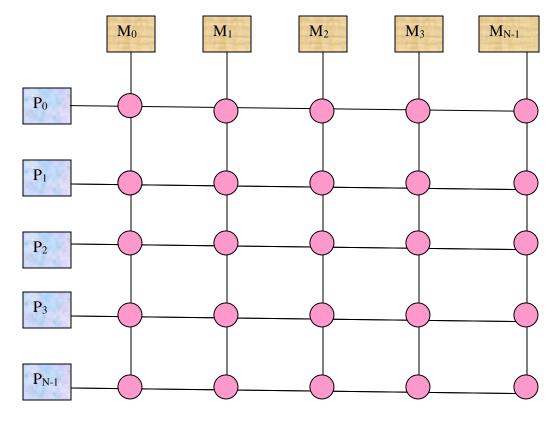

## **Crossbar Connected System:-**

The crossbar itself has no contention. It allows simultaneous access of N processors to N memories, Provided that processor accesses a different memory.

The cross point switch is the source of delay between a processor and memory. When more than one processor attempts to access the same memory at the same time. The crossbar scheme allows high degree of parallelism between unrelated task. It requires  $N^2$  crosspoint switches to fully connect N endpoints to N other end points, such as processors and memory.

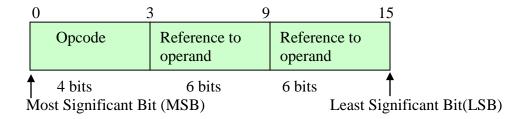

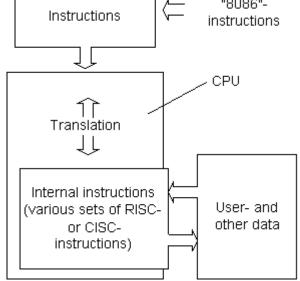

#### **Instruction Set:-Most Important**

It is a collection of all the instructions/commands a CPU can execute. Each instruction consists of several elements.

#### **Elements of Instruction sets:-**

An instruction have following elements.

- An operation code also called opcode which specifies the operation to be performed.

- A reference to the operands on which data processing is to be performed.

- A reference to the operands which may store the results of data processing operation performed by instructions.

- A reference for the next instruction, to be fetched and executed.

#### How is an Instruction represented:-

#### **Types of Instruction:**

- Data Processing Instructions:- (These instructions are used for arithmetic and logic operations in machine)

- Data Storage/Retrieval Instructions :-( These instructions are used load and store instructions)

- Data Movement Instructions:- (These instructions are required to bring in programs and data from various devices to memory or to communicate the results to the input/output devices.)

- Control Instructions:-These instructions are used for testing status of computations through processor status.

- Miscellaneous Instructions :- (These instructions does not fit in any of the above category).

#### **Operand data Types:-**

An operand data types specifies the type on which a particular operation can be performed. Following types of general categories of operand data types.

- Addresses (It is treated as form of data which is used in calculation of actual physical memory address of an operand)

- Numbers (It may be either integers, floating points or decimal numbers)

- Characters ( sequence of characters are called string)

- Logical data types (True 1 or false 0)

#### **Operation Types:-**

- Data transfer Operations.

- Arithmetic Operations.

- Logical & Shift Operations.

- Conversion Operations.

- I/O Operations.

- System Control Operations.

- Transfer Control Operations.

#### **Data transfer operations:-**

#### Example:-

**MOVE or TRANSFER** → Transfer a block of data from source to destination.

Example MOVE R1, R2 or TRANSFER R1, R2

**STORE**—Transfer a word from the processor to a specified location in the main memory.

**LOAD** or **FETCH**→Brings a word from locations of main memory to the processors.

**EXCHANGE** → Exchange the contents of the source with the destination.

**CLEAR or RESET** → Transfer a word containing all 0's to the destination.

**SET**→ Transfer a word containing all 1's to the destination.

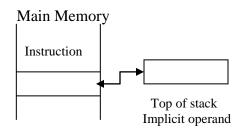

**PUSH**→ Transfer a word from a source to top of stack.

**POP** Transfer a word from top of stack to destination.

#### **Arithmetic operations:-**

Example:-

ADD

**SUBTRACT**

MULTIPLY

DIVIDE

ABSOLUTE  $\rightarrow$  (It convert negative value into positive value)

NEGATE  $\rightarrow$  (It convert given value into negative)

$INCREMENT \rightarrow (It increment value by one)$

DECREMENT→ (It decrement value by one)

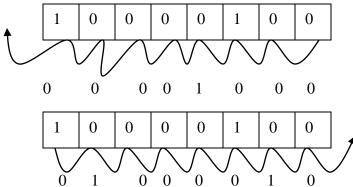

#### **Logical and Shift operations:-**

#### Example:-

AND, OR, NOT, EX-OR, EX-NOR→ (Logical Operator)

LSH (Bit shift left side) → Shift operator RSH (Bit shift right) → Shift operator

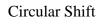

CSH (Bit shift in circular manner) → Shift operator

Let R1=7 and R2=9

R1 = 0000111

R2 = 0001001

R1 AND R2= 0000001 R1 OR R2= 0001111

R1 Ex-OR R2= 0 0 0 1 1 1 0

R1 Ex-NORR2= 1 1 1 0 0 0 1

#### **Conversion operations:-**

TRANSLATE (Translate ASCII to EBCDIC)

CONVERT (Convert one format to other format)

#### **Input/Output operations:-**

**READ (or INPUT)**

WRITE (or OUTPUT)

**TEST I/O**

#### **System Control operations:-**

**OSCALL**:-It is causes the instruction of execution of current program and passes the control to the OS.

#### Transfer of Control operations:-

Branch:-BRP, BRN, BRZ, BRO

Skip:-ISZ

**Subroutine Call:** It is a self contained user program which contains the code often used frequently in large program.

Example:-CALL, RETURN commands are used in subroutine

#### **Addressing Scheme:- Important**

An operand may be specified as the part of the instructions or the reference of the memory location where the value is stored may be given. The addressing scheme refers to the mechanism employed for specifying operands. There are following types of addressing schemes.

• Immediate addressing

Under this scheme, the actual operand D is A, the content of the operand field

D=A

It is used for initialize the value of a variable.

• Direct Addressing:-Under this scheme, the content A of the operand field specify EA,the effective address of the operand

EA = A

D=(EA) Reference of effective address.

Indirect Addressing

Under this addressing scheme the effective address EA and contents of the operand field are related by

• Register Addressing

In this scheme, the instruction specifies the address of the register containing the operand.

Register Indirect Addressing

Under this addressing scheme the operand field specifies the registers which contain the address of the operand.

$$EA=(R)$$

$D=(EA)$

• Displacement addressing

This is very powerful addressing scheme. It combines both the direct as well as the register indirect addressing schemes.

$$EA=A+(R)$$

• Stack addressing scheme:-

In this scheme, the address of an operand is not specified explicitly.

The operand is found on the top of stack. (PUSH and POP operations are performed).

#### Comment:-

All the above addressing schemes are using memory locations and not registers their disadvantage is that the addressable memory location is dependent on the instruction code length i.e., if the code is of n bits the addressable memory is  $2^n$

Allocation of Bits among Opcode and Operand in instruction:-

Some of the factors that are considered for selection of addressing bits.

- Number of addressing modes.

- Number of operands.

- Register addressing versus memory addresses.

- Granularity of address: It implies whether an address is referencing a byte or a word at a time. Example:-

Memory of 8K words (1 word=16 bit)

Word addressing =8K words.  $=2^{3}*2^{10}$  $=2^{13}$  Bytes.

$\rightarrow$ 13 bits are required for <u>Word addressing</u>.

Byte Addressing =2<sup>13</sup>Words. →2<sup>14</sup>Words. →14 bits are required for byte addressing.

#### Commonly Used 8086 Instruction Set

AHC - Add with carry flag ADD - Add two numbers

AND - Bitwise logical AND

CALL - Call procedure or function

CLI - Clear interrupt flag (disable

CBW - Convert byte to word (signed) interrupts)

CWD - Convert word to double word (signed) CMP - Compare two operands

DEC - Decrement by 1

DIV - Unsigned divide

IDIV - Signed divide

IMUL - Signed multiply

IN - Input (read) from port

INC - Increment by 1

INT - Call to interrupt procedure

LEA - Load effective address offset

MOV - Move data

MUL - Unsigned multiply

NOP - No operation

OR - Bitwise logical OR

POP - Pop word from stack

PUSH - Push word onto stack

SAR - Bitwise arithmetic right shift (signed)

NEG - Two's complement negate

NOT - One's complement negate

OUT - Output (write) to port

POPF - Pop flags from stack

PUSHF - Push flags onto stack

SBB - Subtract with borrow

SHL - Bitwise left shift (same as sal)

SHR - Bitwise right shift (unsigned)

STI - Set interrupt flag (enable interrupts)

SUB - Subtract two numbers

TEST - Bitwise logical compare

XOR - Bitwise logical XOR

### AHC: Add with carry flag

Add With Carry Flag

### ADD : Add two numbers

ADD Add two numbers

### AND: Bitwise logical AND

AND Bitwise logical AND

### **CALL**: Call procedure or function

CALL Call procedure or function

### CBW: Convert byte to word (signed)

CBW Convert byte to word (signed)

### CLI : Clear interrupt flag (disable interrupts)

CLI Clear interrupt flag (disable interrupts)

### CWD: Convert word to doubleword (signed)

CWD Convert word to doubleword (signed)

### CMP: Compare two operands

CMP Compare two operands

### DEC: Decrement by 1

DEC Decrement by 1

### DIV: Unsigned divide

DIV Unsigned divide

### IDIV : Signed divide

IDIV Signed divide

### **IMUL**: Signed multiply

IMUL Signed multiply

### IN: Input (read) from port

IN Input (read) from port

### INC: Increment by 1

INC Increment by 1

### **INT**: Call to interrupt procedure

INT Call to interrupt procedure

### IRET: Interrupt return

IRET Interrupt return

### JMP: Unconditional jump

JMP Unconditional jump

### LEA: Load effective address offset

LEA Load effective address offset

### MOV: Move data

MOV Move data

### **MUL**: Unsigned multiply

MUL Unsigned multiply

### NEG: Two's complement negate

NEG Two's complement negate

### NOP: No operation

NOP No operation

### NOT : One's complement negate

NOT One's complement negate

### OUT : Output (write) to port

OUT Output (write) to port

### POP: Pop word from stack

POP Pop word from stack

### POPF: Pop flags from stack

POPF Pop flags from stack

### **PUSHF**: Push flags onto stack

PUSHF Push flags onto stack

### RET: Return from procedure or function

RET Return from procedure or function

### SAL: Bitwise arithmetic left shift (same as shl)

SAL Bitwise arithmetic left shift (same as shl)

### SAR: Bitwise arithmetic right shift (signed)

SAR Bitwise arithmetic right shift (signed)

### **SBB**: Subtract with borrow

SBB Subtract with borrow

### SHL: Bitwise left shift (same as sal)

SHL Bitwise left shift (same as sal)

### SHR: Bitwise right shift (unsigned)

SHR Bitwise right shift (unsigned)

### STI : Set interrupt flag (enable interrupts)

STI Set interrupt flag (enable interrupts)

### **SUB**: Subtract two numbers

SUB Subtract two numbers

### **TEST:** Bitwise logical compare

TEST Bitwise logical compare

### XOR: Bitwise logical XOR

XOR Bitwise logical XOR

### **AAA: ASCII Adjust after Addition**

AAA ASCII Adjust after Addition

### AAD: ASCII Adjust before Division

AAD ASCII Adjust before Division

### **AAM: ASCII Adjust after Multiplication**

AAM ASCII Adjust after Multiplication

### AAS: ASCII Adjust after Subtraction

AAS ASCII Adjust after Subtraction

### **CLC**: Clear carry flag

CLC Clear carry flag

### CLD: Clear direction flag

CLD Clear direction flag

### **CMC**: Complement carry flag

CMC Complement carry flag

### **CMPSB**: Compare bytes in memory

CMPSB Compare bytes in memory

### **CMPSW**: Compare words

CMPSW Compare words

### DAA - Decimal adjust AL after addition

DAA Decimal adjust AL after addition

### DAS: Decimal adjust AL after subtraction

DAS Decimal adjust AL after subtraction

### HLT: Enter halt state

>HLT Enter halt state

### <u>INTO</u>: Call to interrupt if overflow

INTO Call to interrupt if overflow

### LDS: Load pointer using DS

LDS : Load pointer using DS

### LES: Load ES with pointer

LES Load ES with pointer

### **LODSB**: Load string byte

LODSB Load string byte

### **LODSW**: Load string word

LODSW Load string word

### LOOP: Loop control

LOOP Loop control

### LOOPE: Loop control

LOOPE : Loop control

### **LOOPNE**

LOOPNE

### LOOPNZ: Loop control

LOOPNZ : Loop control

### **LOOPZ**: Loop control

LOOPZ : Loop control

### LEA: Load Effective Address

LEA Load Effective Address

### LES: Load ES with pointer

LES : Load ES with pointer

### **LODSB**: Load string byte

LODSB Load string byte

### LODSW: Load string word

LODSW : Load string word

### **LOOP**

LOOP

### **ROL**: Rotate left

ROL Rotate left

### **ROR**: Rotate right

ROR Rotate right

## **SAHF**: Store AH into flags

SAHF Store AH into flags

### STC : Set carry flag

STC Set carry flag

### STD: Set direction flag

STD Set direction flag

### STOSB: Store byte in string

STOSB Store byte in string

### **STOSW**: Store word in string

STOSW Store word in string

### XCHG: Exchange data

XCHG: Exchange data

#### **Basic Structure of CPU:-**

CPU basically consists of ALU and CU.

ALU:-It may perform all types of arithmetical and logical operations.

CU:-It is heart of computer which may perform controlling operations inside CPU.

There are following types of registers basically used in processor.

- AC (Accumulator):-It interacts with ALU and stores the input or output operand.

- DR (Data register):-It act as buffer between main memory and CPU.

- PC (Program Counter):-It contains the address of next instructions word to be executed.

- IR (Instruction Register):-It holds the current instructions.

- MAR (Memory Address Register):-It is used to provide address of memory location from where data is to be retrieved or to which data is to be stored.

#### **Register Organization of CPU:-**

There are basically two categories of registers.

• Programmer visible registers:-